Découvrez les mémoires statiques et dynamiques

Après avoir étudié l'architecture générale des mémoires dans le chapitre précédent, vous découvrirez ici deux types de mémoires : statique et dynamique.

Découvrez le point mémoire statique SRAM

La mémoire statique, encore appelée "Random Access Memory - 6 Transistors" (RAM-6T) est basée sur un circuit de 2 inverseurs rebouclés, qui assurent le stockage de deux états stables, 0 ou 1. Deux transistors supplémentaires servent de système de lecture ou d'écriture suivant le cycle choisi. Le schéma comporte au total 6 transistors, comme indiqué à la figure ci-dessous.

On remarquera que la cellule stocke la donnée Data et son inverse ~Data. Cela implique d'écrire en même temps (lors du cycle d'écriture) Data, par le biais de BitLine et ~Data, par le biais de ~BitLine.

Point mémoire à 6 transistors - WordLine=ligne de mot, BitLine=ligne de donnée

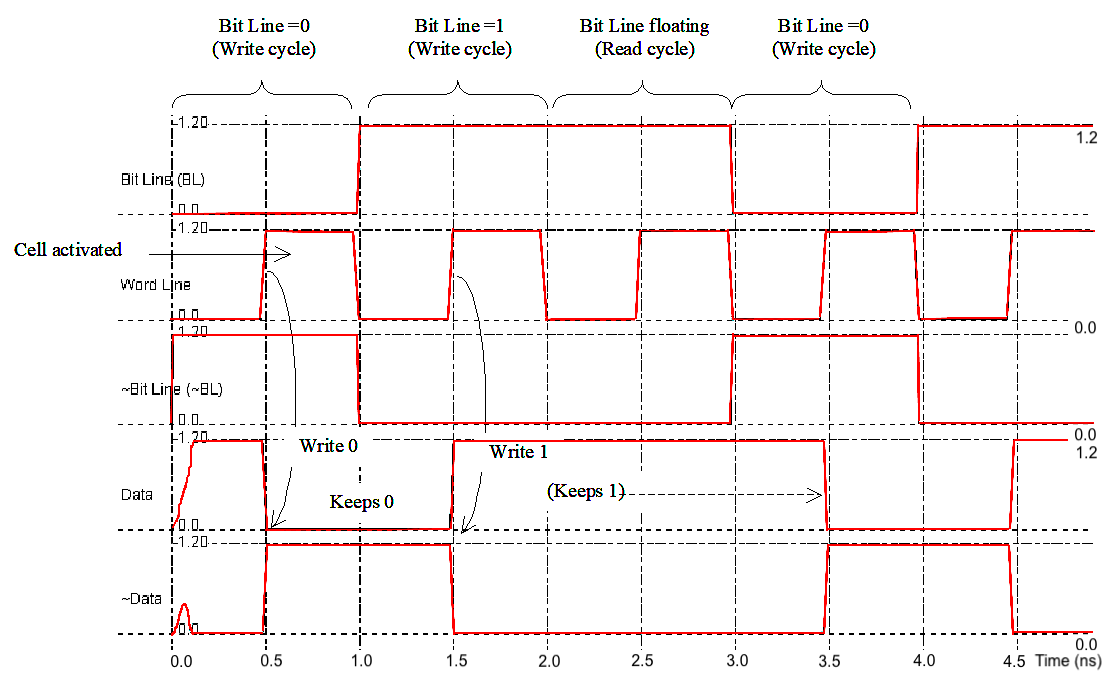

La simulation de la phase d'écriture dans la cellule RAM est proposée à la figure ci-dessous. Les données à écrire sont imposées sur BitLine (0,1,10..), et l'inverse sur ~BitLine (1,0,0,1). Comme WordLine est à 0, la cellule est isolée de l'extérieur ; en effet les deux transistors de passage NMOS sont coupés. Data atteint une valeur de 1, ~Data atteint 0, la mémoire stocke donc la valeur "1".

Au temps 0.5ns, WordLine passe à 1, la cellule mémoire est alors connectée à BitLine et ~BitLine. Les valeurs imposées modifient la valeur interne de la mémoire, Data passe alors à 0 et ~Data à 1.

À l'instant 1.0ns, WordLine passe à 0, la mémoire est de nouveau isolée.

À l'instant 1.5ns, WordLine passe à 1, la cellule de mémoire est à nouveau sélectionnée. L'information à stocker est maintenant 0 sur BitLine et 1 sur ~BitLine. Après un très court délai d'écriture (de l'ordre de quelques pico-secondes), Data passe à 1 et ~Data à 0.

Simulation de la mémoire statique - La cellule est activée pour WordLine=1. Le cycle d'écriture correspond à t=0..2ns, le cycle de lecture de 2..4ns

Plan mémoire statique

La cellule mémoire de base a été conçue pour être dupliquée en X et Y afin de faire cohabiter un grand nombre de cellules, autant dans le sens horizontal que dans le sens vertical. Un arrangement modeste de 4 x 4 cellules RAM est proposé à la figure ci-dessous. Les lignes de sélection WL[i] concernent toutes les cellules d'une même ligne. Les lignes de bits BL[j] et nBL[j] concernent toutes les cellules d'une même colonne.

Mémoire 4 x 4 bits en matrice de cellules à 6 transistors

L'architecture complète de cette mémoire comporte, comme étudié dans le chapitre précédent, un décodeur de ligne, un décodeur de colonne ainsi qu'un circuit de lecture/écriture.

Découvrez le point mémoire dynamique DRAM

La mémoire RAM dynamique ne comporte qu'un seul transistor, au lieu de 6 dans la cellule mémoire statique décrite à la section précédente. Une telle simplification permet une amélioration considérable de la densité de la matrice mémoire. L'élément de stockage n'est plus la boucle de deux inverseurs, intrinsèquement stable, mais seulement un condensateur Cs, également appelé condensateur de stockage.

Celui-ci n'est pas stable comme la cellule statique, mais permet de garder une information sous forme de charges dans le condensateur pendant une durée relativement longue (à l'échelle des commutations dans les circuits intégrés, qui sont de l'ordre de la picoseconde), c'est-à-dire quelques millisecondes.

Cycle d'écriture de la mémoire dynamiqueL’architecture des cellules DRAM est illustrée dans la figure ci-dessous, en montrant l'opération d'écriture et de maintien d'une information logique "1". La donnée à écrire est imposée sur la ligne BL (BL=1), la ligne WL est alors activée (WL=1), le transistor NMOS devient passant et Cs se charge à "1" (VDD-Vt). Lorsque WL est inactif (WL=0), le condensateur de stockage Cs conserve le "1" (VDD-Vt) pendant quelques millisecondes avant de se décharger inéluctablement à cause des courants de fuite.

Cycle d'écriture d'une information "1" dans la mémoire RAM dynamique

Comme le transistor de transfert est de type NMOS, la valeur analogique stockée dans la capacité n'est pas exactement "1" mais (VDD-Vt), où Vt est la tension de seuil (soit 0.7V au lieu de 1V).

Si l'on désire stocker un "0", on impose 0 sur BL, on active WL, ce qui a pour effet de décharger Cs (figure ci-dessous). Ensuite, l'information "0" reste une fois WL désactivé. La capacité Vs conserve le "0" (0 V) pendant quelques millisecondes.

Cycle d'écriture d'une information "0"

Les courants de fuite de la capacité dégradent progressivement la tension stockée dans Cs. Il est donc nécessaire de "rafraîchir" l'information à intervalles réguliers, afin de ne pas perdre la donnée. Pour cela, on réitère fréquemment le cycle d'écriture en imposant toujours la même valeur à écrire.

Une fois les données écrites dans les cases mémoires, on peut venir lire ces données.

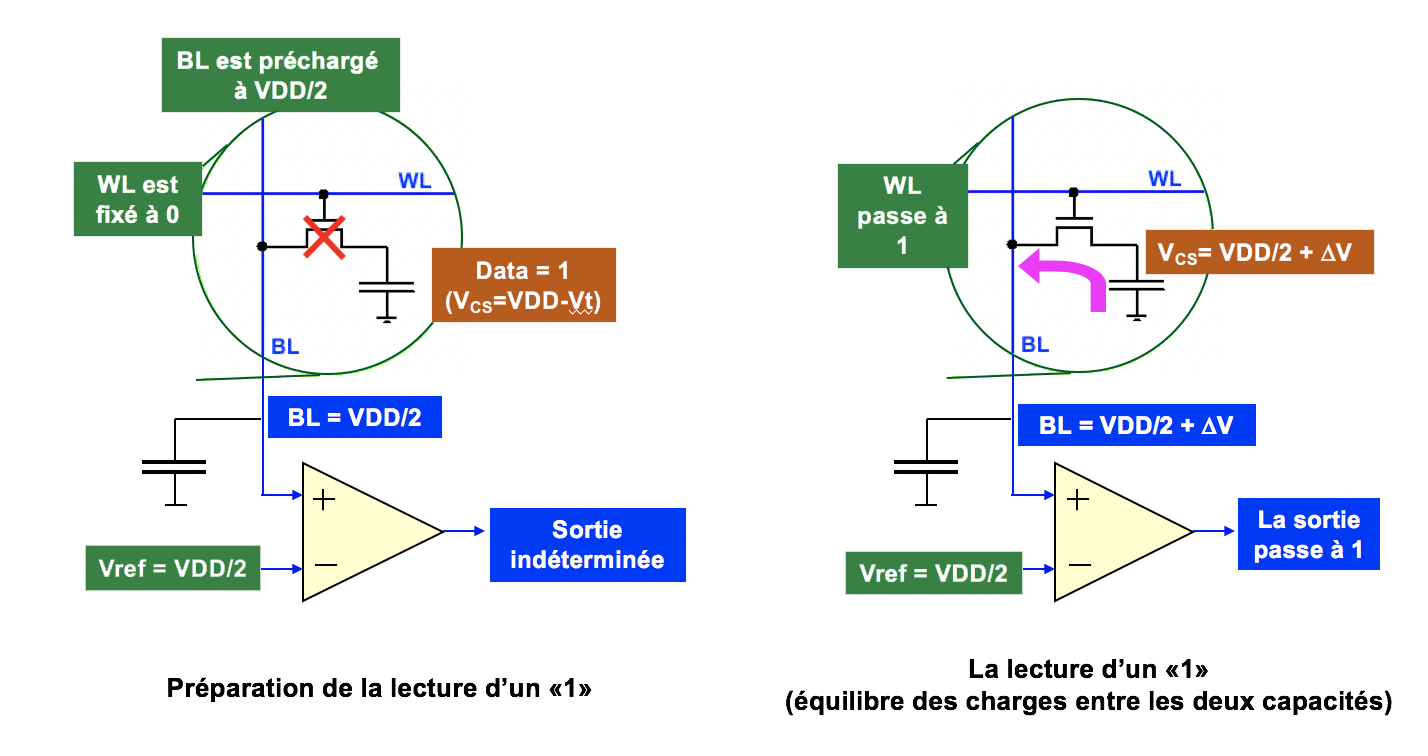

La lecture se déroule en plusieurs étapes (exemple de la lecture d'un "1") :

- La première étape (figure de gauche) consiste à précharger la ligne BL à VDD/2, c'est-à-dire à mi-chemin entre "0" et "1". WL reste à 0 afin que le transistor NMOS soit coupé et la donnée "1" piégée dans Cs.

- BL qui a été initialement chargée à VDD/2 est maintenant rendue flottante. Lorsque WL est activée (figure de droite), une communication est établie entre BL et le condensateur Cs à travers le transistor NMOS passant.

- Les charges se partagent entre la capacité de stockage Cs et la capacité CBL de la ligne BL. Il en résulte une légère augmentation au-dessus de VDD/2 de la tension VBL, grâce à l'injection des charges depuis la cellule mémoire.

- Si Cs contient "0", BL étant préchargé à VDD/2, le résultat de l'écriture sera une légère diminution de la tension de BL.

Exemple de lecture d'un "1"

Le cycle de lecture est destructif pour les informations stockées. En effet, au moment de la lecture, il y a répartition des charges dans les deux capacités, celle de stockage et celle du bus BL, ce qui modifie la tension aux bornes de Cs.

Juste après la lecture, il faut donc toujours réécrire la donnée dans Cs.

Le point mémoire DRAM est principalement un transistor et une capacité. La fabrication de la capacité fait appel à des étapes de process dédiées, notamment avec l'utilisation de diélectriques à forte permittivité tels que Ta2O5 (permittivité 23 au lieu de 4 pour SiO2), afin de maximiser la valeur de la capacité Cs. Ceci a pour effet d'augmenter la durée de stockage ainsi que les variations de tension lors du cycle de lecture. Un exemple de capacités fabriquées par TSMC en process 65-nm est donné ci-dessous.

Mémoire DRAM intégrée du process TSMC 65-nm Copyright © Taiwan Semiconductor Manufacturing Company Limited 2010-2019, All Rights Reserved.

Découvrez le point mémoire flash

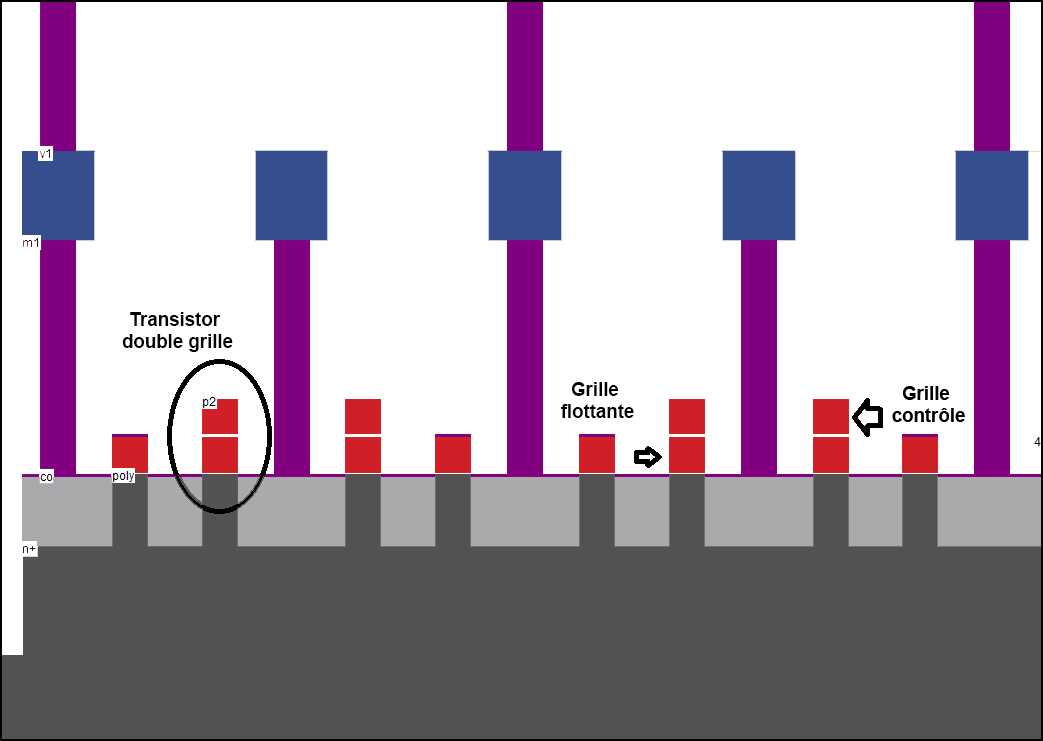

L'élément de base d'une mémoire FLASH est un transistor à double grille, dont l'une est flottante (figure ci-dessous). Le concept repose sur la possibilité de piéger des électrons dans la grille totalement isolée, qui est situé entre la grille de contrôle et le canal. Les charges qui se trouvent dans cette grille flottante ont un impact direct sur les performances du transistor équivalent :

- Lorsqu'il n'y a pas de charge piégée dans la grille flottante (figure en haut), un courant important peut circuler entre la source et le drain. Il suffit d'appliquer "1" sur la grille, comme un transistor canal N standard.

- Lorsque des charges sont piégées dans la grille flottante (figure en bas), le courant circulant dans le dispositif est quasi nul, indépendamment de la tension de grille.

Les électrons piégés dans la grille flottante empêchent la création du canal, le transistor est équivalent à un circuit ouvert.

La rétention de données est une caractéristique essentielle de la mémoire FLASH. Elle doit être garantie dans une large gamme de températures et de conditions de fonctionnement. La rétention de données d'une mémoire FLASH, correspondant à la rétention des charges dans la grille flottante, est d'environ 10 ans.

Simulation du transistor double grille de la mémoire Flash : grille flottante déchargée (en haut) ou chargée avec des électrons (en bas)

Le concept de mémorisation d'un 1 ou d'un 0 réside dans le fait d'être en présence, ou non, d'un transistor avec charges piégées dans sa grille flottante. En testant les performances de ce transistor, on en déduit la présence, ou non, des charges et on attribue donc deux états différents 1 ou 0.

Vue en coupe d'un plan mémoire FLASH

La figure ci-dessus montre une vue en coupe d'un plan mémoire FLASH. On distingue les transistors à double grille avec deux zones rouges empilées. La zone la plus proche du canal est flottante, la zone la plus haute permet le contrôle du transistor. A côté de chaque transistor double-grille se trouve un transistor "normal", à une seule grille, qui sert de transistor d'accès comme dans la cellule DRAM.

La cellule composée d'un transistor double grille et d'un transistor d'accès est la plus simple et la plus robuste (Single-Level-Cell). Ce n'est cependant pas la plus compacte. Des architectures appelées FLASH NAND et NOR permettent d'intégrer plus de cellules mémoires dans un même espace, au prix d'une fiabilité moins grande et de restrictions de programmation.

La charge et décharge de la grille flottante s'effectue par application de tensions très élevées sur la grille de contrôle (typiquement 12V) ou sur le drain pendant environ 1µs, ce qui a pour effet de piéger ou d'évacuer des électrons, grâce à l'effet tunnel.

Le nombre de cycles d'écriture d'une mémoire FLASH est limité, à cause de la destruction progressive de l'oxyde de grille entraîné par l'effet tunnel. Les mémoires FLASH les plus robustes sont capable de supporter 100 000 cycles d'écriture, tandis que les mémoires FLASH les plus fragiles supportent moins de 500 cycles d'écriture.

Découvrez le point mémoire ROM

Un point mémoire ROM permet de stocker une valeur "0" ou "1", qui est programmée à l'avance (au moment de la fabrication de la mémoire) et ne peut plus être modifiée. Un principe simple d'architecture ROM consiste à positionner ou non un transistor sur une matrice d'accès, avec WL en guise de commande, et BL en guise de donnée en lecture, comme indiqué ci-dessous. Si le transistor est présent, BL passe à 0, sinon, BL reste à sa valeur chargée au préalable (ici à VDD quand Precharge=0).

Exemple de mémoire ROM 8x8 - 8 fils WordLine à gauche, 8 fils BL en bas

Il est possible de rentrer des informations numériques telles que du code machine, des valeurs numériques, ou encore des clés de chiffrement grâce à ces mémoires. La structure en matrice 8 lignes x 8 colonnes correspond ici à 8 octets de données, chaque octet pouvant être lu en sélectionnant une ligne WL[i] parmi 8. Dans l'exemple ci-dessus, WL=1, les données sur BL[0..7] correspondent à 0b10010111, soit 0x97, où la donnée "1" correspond à une absence de transistor à l'intersection WL[i]/BL[j], et la donnée "0" à la présence d'un transistor à l'intersection WL[i]/BL[j].

Dans les chapitres précédents, vous avez eu un aperçu des différentes mémoires couramment utilisée. Nous vous proposons maintenant de mettre en œuvre vos connaissances pour concevoir par vous même sur DSCH une mémoire 8x8.